ساختار حافظه و آدرس دهی واحدهای جانبی

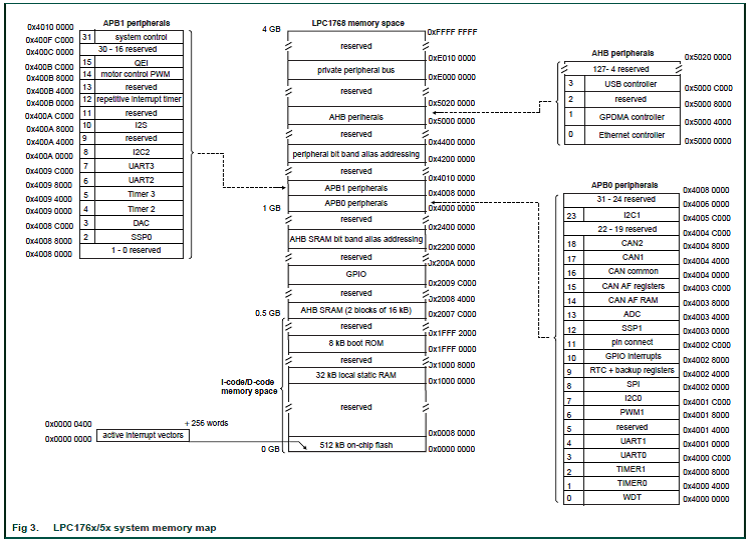

میکروکنترلر LPC1768 دارای باس آدرس 32 بیتی است و بر اساس آن می تواند 4G آدرس دهی نماید. حافظه های مختلف و آدرس واحدهای جانبی همگی در این فضا قرار دارند. شکل 3 توزیع حافظه را نشان می دهد.

حافظه FlashROM که یک حافظه برای کد برنامه کاربردی و یا برنامه بوت است، در دو بخش این فضا قرار دارد. قسمت آول در ابتدای حافظه از آدرس 0x00000000 تا آدرس 0x00080000 با حجم 512kB است. این حافظه برای ذخیره کد دستورالعمل ها و داده های ثابت می باشد. پروگرام کردن این حافظه به روشهای مختلف، از جمله پورت سریال انجام می شود. در حالیکه برنامه کاربردی در حال اجرا است، برنامه کاربردی می تواند حافظه Flah را پاک یا پروگرام نماید. این امر انعطاف پذیری بالایی در بروزکردن برنامه کاربردی و داده های آن به ما می دهد.

همانطور که می بینید جدول بردارهای وقفه می تواند، در ابتدای این حافظه قرار گیرد. امکان جابجا کردن جدول بردارهای وقفه نیز وجود دارد. انتقال جدول توسط رجیستر آفست جدول وقفه (Vector Table Offset Register = VTOR) انجام می شود. این جدول 256 کلمه ای ( 1024 بایتی ) در هر کجای 1GB اول حافظه می تواند قرار داده شود.

بخش دوم مربوط به برنامه بوت است، که از آدرس 0x1FFF0000 تا آدرس 0x1FFF2000 با حجم 8 kB می باشد.

میکروکنترلر LPC176x/5x حداکثر دارای 64 kB حافظه RAM است. این حافظه از طریق باس های با سرعت بالا توسط پردازشگر مرکزی و DMA قابل دسترسی هستند. حافظه RAM برای ذخیره موقت داده ها در طول برنامه به کار می رود.

در LPC1768 که دارای 64 kB حافظه RAM است. این حافظه در سه قسمت قرار دارند. بخش اول با حجم 32 kB از آدرس 0x1000 0000 تا آدرس 0x1000 7FFF قرار دارد. بخش دوم با حجم 16 kB از آدرس 0x2007 C000 تا آدرس 0x2007 FFFF با نام بانک 0 است و بخش سوم با حجم 16 kB از آدرس 0x2008 0000 تا آدرس 0x2008 3FFF با نام بانک 1 است.

همانطور که در شکل 2 می بینید، این 3 حافظه ، 3 باس جداگانه دارند. این معماری امکان دسترسی CPU و DMA را به طور جداگانه و با کمترین / بدون تاخیر به حافظه ها را می دهد.

در LPC17xx واحدهای جانبی در فضای حافظه در نظر گرفته شده اند. فضای 2 MB برای حداکثر 128 واحد جانبی در نظر گرفته شده است. با اینکار برای هر واحد جانبی 16 kB فضا در نظر گرفته شده است. اینکار باعث ساده شدن، دیکد آدرس واحدهای جانبی می شود. تمام آدرس های رجیسترهای واحدهای جانبی به کلمه 32 بیتی، اشاره می کنند. به این ترتیب امکان خواندن و یا نوشتن به صورت بایت یا نیم کلمه، در این رجیسترها میسر نیست.

آدرس های واحدهای جانبی در جدول 4 آمده است. هیچکدام از واحدهای جانبی از تمام فضای 16 kB تخصیص داده شده استفاده نمی کنند.

Flash accelerator

بلوک شتابدهنده فلش برای افزایش کارآیی پردازشگر Cortex-M3 در زمان اجرای کد از حافظه فلش است. علاوه بر آن در کاهش توان مصرفی نقش دارد. شتابدهنده فلش همچنین در بهبود سرعت و توان در دسترسی به داده های حافظه فلش موثر است.

بلوک دیاگرام شتاب دهنده فلش در شکل 13 آمده است. شتاب دهنده فلش دارای بخش های زیر است:

- واسط باس AHB برای دسترسی به باس های کد دستورالعمل (I-code) ، باس داده دستورالعمل (D-code) و کنترلر DMA

- 8 بافر 128 بیتی

- بخش کنترل حافظه فلش و مقایسه آدرس

- واسط با حافظه فلش

شتاب دهنده فلش با رجیستر FLASHCFG کنترل می شود.

|

آدرس |

مقدار اولیه |

دسترسی |

شرح عملکرد |

نگارش |

|

0x400F C000 |

0x303A |

R/W |

این رجیستر برای تنظیم زمان دسترسی به حافظه فلش است. |

FLASHCFG |

رجیستر FLASHCFG برای تنظیم زمان دسترسی به حافظه فلش مطابق جدول 49 می باشد. 12 بیت پایین این رجیستر نباید تغییر داده شود. پس از ریست کار شتاب دهنده فلش شروع و زمان پیش فرض دسترسی به حافظه 4 پالس ساعت است.

تغییر در رجیستر FLASHCFG باعث می شود، شتاب دهنده فلش تمام مقادیر لچ ها را خراب کند، پس لازم است اطلاعات فلش دوباره خوانده شود. این امر هماهنگی شتاب دهنده فلش با پردازشگر را تضمین می کند.

به زبان ساده، شتاب دهنده فلش تلاش می کند تا دستورالعمل بعدی مورد نیاز را در بافرهای خود داشته باشد. شتاب دهنده فلش دارای 8 بافر 128 بیتی برای ذخیره دستورالعمل ها و داده ها است. هر بافر 128 بیتی قادر است 4 دستورالعمل 32 بیتی، 8 دستورالعمل 16 بیتی و یا تلفیقی از این دو را در خود نگهداری کند. در زمان اجرای دستورالعمل ها، یک بافر دربردارنده دستورالعمل و یک خط کامل حافظه فلش مربوط به این دستورالعمل است و یا در بردارنده یک خط حافظه فلش شامل آدرس است. بافرها بر اساس چگونگی استفاده به عنوان دستورالعمل یا داده و همینطور زمانیکه باید استفاده شوند، علامت گذاری می شوند. این اطلاعات برای جایگزینی بافرها لازم است.

هر دسترسی به فضای آدرس حافظه فلش به شتاب دهنده فلش ارائه می شود. اگر یک درخواست واکشی دستورالعمل از فلش و درخواست داده از فلش به طور همزمان داده شود، سوئیچ ماترس اولویت را به درخواست داده می دهد. چون ممانعت از دسترسی به داده باعث کاهش سرعت اجرا می شود، در حالیکه ممانعت از واکشی دستورالعمل باعث کاهش سرعت اجرا نمی شود. پس از دسترسی به داده فلش، واکشی و زود واکشی (Prefetch) می تواند دنبال شود.

پرش ها و یا تغییر روند برنامه باعث قطع ترتیب واکشی دستورالعمل به شرح بالا می شود. استراتژی جایگزینی بافرها، بگونه ای انجام می شود که از اطلاعات موجود استفاده شود.

اگر غیر از روش عادی پروگرام کردن حافظه فلش، سعی در نوشتن مستقیم در حافظه فلش گردد ( مانند توابع بوت ROM )، شتاب دهنده فلش اعلان وضعیت خطا خواهد کرد.

شرح رجیستر پیکربندی شتاب دهنده فلش Flash Accelerator Configuration register (FLASCFG – 0x400F C000)

|

مقدار اولیه |

دسترسی |

شرح عملکرد |

مقدار |

نگارش |

بیت |

|

0x03A |

|

رزرو : کاربر نباید مقدار این بیت را از مقدار اولیه تغییر دهد. |

- |

- |

11:0 |

|

0x3 |

- |

مقدار این 4 بیت بعلاوه یک، تعداد پالس ساعت پردازشگر برای دسترسی به حافظه فلش را تعیین می کند. توجه : تنظیم نادرست این مقدار، ممکن است باعث عملکرد نادرست میکروکنترلر شود. |

|

FLASHTIM |

15:12 |

|

|

|

دسترسی به فلش در یک پالس ساعت پردازشگر انجام می شود. برای مواردی که فرکانس پالس ساعت پردازشگر کمتر از 20MHz است، استفاده شود. |

0000 |

||

|

|

|

دسترسی به فلش در دو پالس ساعت پردازشگر انجام می شود. برای مواردی که فرکانس پالس ساعت پردازشگر کمتر از 40MHz است، استفاده شود. |

0001 |

||

|

|

|

دسترسی به فلش در سه پالس ساعت پردازشگر انجام می شود. برای مواردی که فرکانس پالس ساعت پردازشگر کمتر از 60MHz است، استفاده شود. |

0010 |

||

|

|

|

دسترسی به فلش در چهار پالس ساعت پردازشگر انجام می شود. برای مواردی که فرکانس پالس ساعت پردازشگر کمتر از 80MHz است، استفاده شود. |

0011 |

||

|

|

|

دسترسی به فلش در پنج پالس ساعت پردازشگر انجام می شود. برای مواردی که فرکانس پالس ساعت پردازشگر کمتر از 100MHz است، استفاده شود. فقط در میکروکنترلرهای LPC1759 و LPC1769 تا 120MHz نیز استفاده می شود. |

0100 |

||

|

|

|

دسترسی به فلش درشش پالس ساعت پردازشگر انجام می شود. این حالت برای تمام شرایط می تواند استفاده شود. |

0101 |

||

|

|

|

برای قطعات جدید با سرعت بیشتر در نظر گرفته شده است. |

Other |

||

|

NA |

|

رزرو : کاربر نباید در این بیت ها یک بنویسد و خواندن از این بیت ها مقدار معتبری را به ما نمی دهد. |

- |

- |

31:16 |