این بخش مدل برنامه Cortex-M3 را شرح می دهد. علاوه بر شرح رجیسترهای هسته، در مورد مودهای پروسسور و سطح های ممتاز (Privilege) اجرای نرم افزار و استک صحبت می کند.

- مد پروسسور و سطح های ممتاز اجرای نرم افزار

مدهای پروسسور عبارتند از:

- حالت ترد (Thread) : برای اجرای نرم افزار کاربردی استفاده می شود. پروسسور پس از خارج شدن از ری ست وارد حالت ترد می شود.

- حالت هندلر (Handler) : برای اجرای استثنا ها استفاده می شود. پروسسور پس از اتمام استثنا به حالت ترد برمی گردد.

حالت های ممتاز برای اجرای نرم افزار عبارتند از:

1- غیر ممتاز (UnPrivilege) :

- نرم افزار در دسترسی به دستورالعملهای MSR و MRS محدود است و از دستورالعمل CPS نمی تواند استفاده کند.

- نرم افزار به تایمر سیستم، NVIC و بلوک کنترل سیستم دسترسی ندارد.

- نرم افزار ممکن است در دسترسی به حافظه و تجهیزات جانبی محدود باشد.

نرم افزار غیر ممتاز در مد غیر ممتاز اجرا می شود.

2- ممتاز (Privilege)

- نرم افزار از تمام دستورالعملها می تواند استفاده کند و به همه منابع دسترسی دارد.

نرم افزار ممتاز در مد ممتاز اجرا می شود.

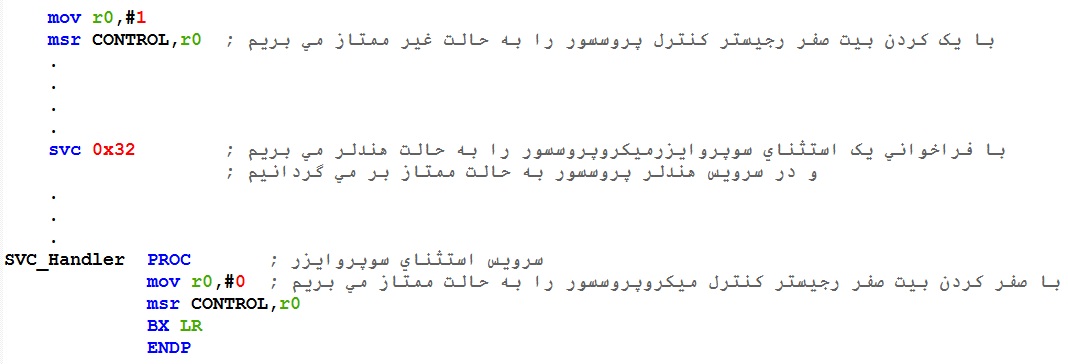

در مد ترد ، حالت ممتاز یا غیر ممتاز به کمک بیت 0 رجیستر کنترل تعیین می شود. در حالت هندلر اجرای نرم افزار همواره در حالت ممتاز است.تنها نرم افزار ممتاز می تواند، در رجیستر کنترل برای تغییر سطح ممتاز بنویسد و اجرای نرم افزار را به حالت غیرممتاز ببرد. نرم افزار غیر ممتاز نمی تواند با نوشتن در رجیستر کنترل (Control) ، اجرا را به حالت ممتاز ببرد. برای رفتن از حالت غیرممتاز به حالت ممتاز باید از دستورالعمل (SVC (supervisor call استفاده کرد. دستورالعمل SVC یک استثنا را فراخوانی می کند و در "سرویس استثنا سوپروایزر" با نوشتن در رجیستر کنترل به حالت ممتاز می توان رفت.

در مثال زیر نحوه بردن میکروپروسسور به حالت غیر ممتاز Unprivilege و بر گرداندن آن به حالت ممتاز Privilege به کمک استثنای SVC نشان داده شده است.

Stacks

استک در اینجا نیز برای ذخیره آدرس برگشت در هنگام فراخوانی زیربرنامه ها، تابع ها و یا اجرای وقفه و استثناها بکار می رود. علاوه بر آن از استک برای ذخیره رجیسترها به طور موقت به خصوص در هنگام جابجاشدن بین زیربرنامه ها و یا سرویس ها (Task Switch) استفاده می شود. در اینجا هرگاه داده ای در استک بخواهد push شود، ابتدا از SP کم و سپس در خانه ای که SP اشاره می کند، نوشته می شود. پروسسور دارای دو استک است. استک اصلی و استک پروسس و هر کدام دارای SP مستقل هستند.

در حالت ترد بیت 1 رجیستر Control مشخص می کند، که پروسسور از کدام SP استفاده کند. در حالت هندلر پروسسور همواره از استک اصلی استفاده می کند و نمی توان آن را تغییر داد.

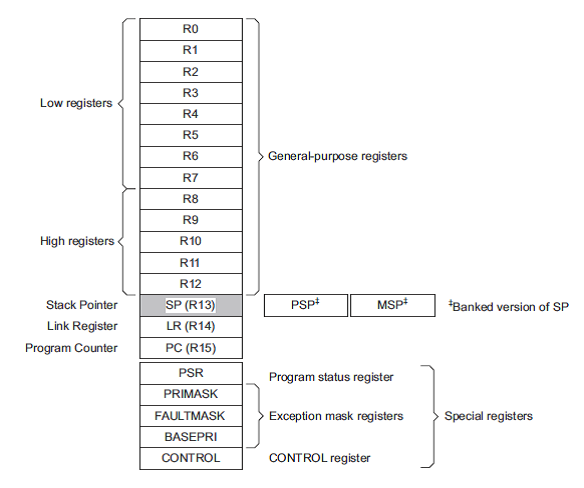

رجیسترهای هسته :

رجیسترهای هسته در شکل زیر آمده اند.

رجیسترهای همه منظوره : رجیسترهای R0-R12 رجیسترهای 32 بیتی همه منظوره هستند و برای عملیات داده استفاده می شوند.

اشاره گر استک : رجیستر R13 به عنوان SP است. همانطور که در شکل مشخص است، ما دو SP داریم. در حالت ترد بیت [1] رجیستر Control مشخص می کند، کدام SP استفاده می شود.

0 – اشاره گر استک اصلی (MSP) – در هنگام ریست این استک استفاده می شود.

1 – اشاره گر استک پروسس (PSP)

در هنگام ریست پروسسور مقدار MSP را از آدرس 0x00000000 بر می دارد.

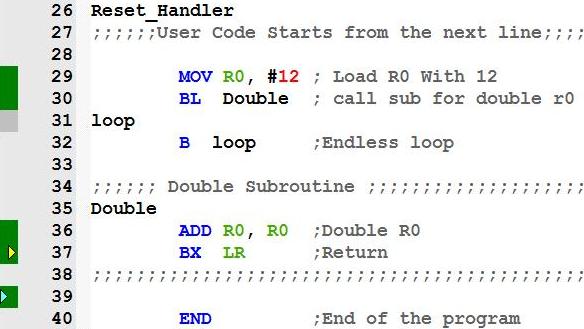

رجیستر لینک : رجیستر R14 به عنوان LR است. این رجیستر اطلاعات برگشت از زیربرنامه ها، توابع و استثنا ها را ذخیره می کند. در هنگام ریست پروسسور LR را با مقدار 0xFFFFFFFF بار می کند.

شما با دستورالعمل BL یک زیربرنامه را به شکل زیر صدا می زنید: BL Sub1

آنچه در اینجا اتفاق می افتد، ذخیره دستورالعمل بعدی ( آدرس برگشت ) در رجیستر LR و بار شدن PC با آدرس زیربرنامه Sub1 است. مثال زیر را ببینید.

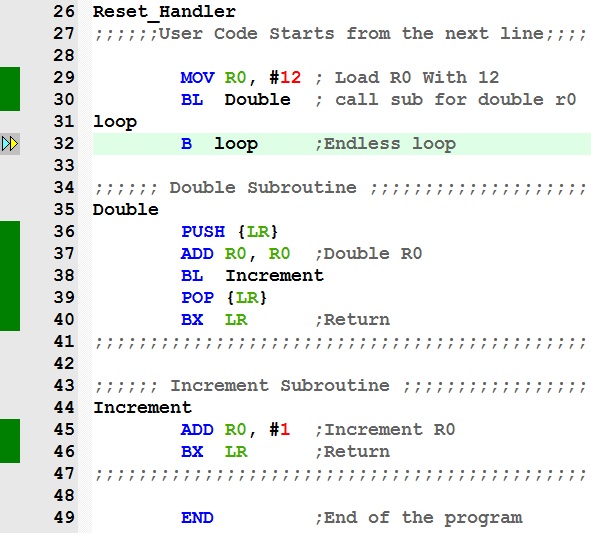

اما اگر در داخل زیربرنامه بخواهید، زیربرنامه دیگری را اجرا کنید، باید قبل از صدا زدن زیربرنامه دوم مقدار LR را در استک ذخیره کنید، وگرنه LR ( آدرس برگشت به زیربرنامه اول ) خراب می شود. مثال زیر در مورد صدا زدن یک زیربرنامه در داخل یک زیربرنامه دیگر است. اینکار می تواند ادامه داشته باشد.

شمارنده برنامه (PC) : رجیستر R15 همان شمارنده برنامه است. مقدار PC برابر آدرس دستورالعمل جاری است. بیت 0 آن به دلیل اینکه دستوالعمل ها نیم کلمه ای هستند همواره 0 است. در هنگام ریست، پروسسور رجیستر PC را با بردار ریست که در آدرس 0x00000004 قراردارد، بار می کند.

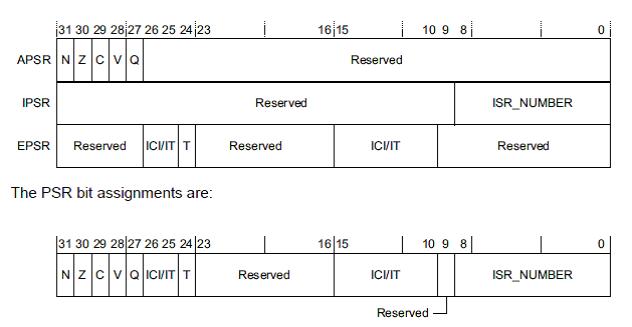

رجیستر وضعیت برنامه PSR : رجیستر PSR از ترکیب سه رجیستر تشکیل می شود:

- رجیستر وضعیت برنامه کاربردی (APSR)

- رجیستر وضعیت برنامه وقفه (IPSR)

- رجیستر وضعیت برنامه اجرا (EPSR)

این سه رجیستر دارای بیت های متفاوتی از رجیستر PSR هستند، بگونه ای که از ترکیب سه رجیستر به PSR می رسیم. شکل زیر سه رجیستر را به تنهایی و تلفیق آن ها را نشان می دهد.

دسترسی به هر کدام از رجیسترهای فوق به تنهایی و یا دو تا از سه رجیستر و یا سه رجیستر به صورت همزمان به شکل جدول 628 میسر است. فقط باید در نام آن دقت کنیم.

دسترسی به هر کدام از رجیسترهای فوق به تنهایی و یا دو تا از سه رجیستر و یا سه رجیستر به صورت همزمان به شکل جدول 628 میسر است. فقط باید در نام آن دقت کنیم.

برای خواندن و نوشتن در این رجیسترها از دستورالعمل های MRS و MSR با آرگومان مناسب استفاده می شود.

MRS برای خواندن رجیسترهای خاص به شکل مقابل استفاده می شود: MRS {cond} Rd, spec_reg

Cond به صورت اختیاری یک شرط می تواند باشد.

Rd رجیستر مقصد است.

Spec_reg هر کدام از رجیسترهای APSR, IPSR, EPSR, IEPSR, IAPSR, EAPSR, PSR, MSP, PSP, PRIMASK, BASEPRI, BASEPRI_MAX, FAULTMASK, یا Control می تواند باشد.

مثال : MRS R0,IEPSR

MSR برای نوشتن در رجیسترهای خاص به شکل مقابل استفاده می شود : MSR{cond} spec_reg, Rn

Cond به صورت اختیاری یک شرط می تواند باشد.

Rn رجیستر مبدا است.

Spec_reg هر کدام از رجیسترهای APSR, IPSR, EPSR, IEPSR, IAPSR, EAPSR, PSR, MSP, PSP, PRIMASK, BASEPRI, BASEPRI_MAX, FAULTMASK, یا Control می تواند باشد.

مثال : MRS IEPSR,R0

حال به سراغ معرفی بیشتر این سه رجیستر می رویم:

رجیست وضعیت برنامه کاربردی (APSR) :

این رجیستر وضعیت فلگ های ایجاد شده از اجرای دستورالعمل قبل را در بر دارد. آرایش بیت ها در این رجیستر به شکل زیر است:

فلگ منفی (N) : مبین اینست که نتیجه عمل منفی است و یا در مقایسه عملوند اول از دوم کمتر بوده است.

فلگ صفر (Z) : مبین اینست که نتیجه عمل صفر شده و یا در مقایسه دو عملوند مساوی بوده اند. توجه داشته باشید اگر نتیجه صفر شود، این فلگ 1 می شود.

فلگ کری (C) : هرگاه در عمل کری ایجاد شود.

فلگ سرریز (V) : هرگاه نتیجه عمل از محدوده مجاز خارج شود. ( از حداکثر مثبت بیشتر و یا از حداقل منفی کمتر شود).

فلگ اشباع (Q) : اگر در دستورالعملهای SSAT یا USAT نتیجه برگشتی از دستورالعمل با مقدار اولیه متفاوت باشد، در این حالت اشباع رخ داده است و این فلگ 1 می شود. برای 0 کردن این فلگ باید از دستورالعمل MSR استفاده کنید.

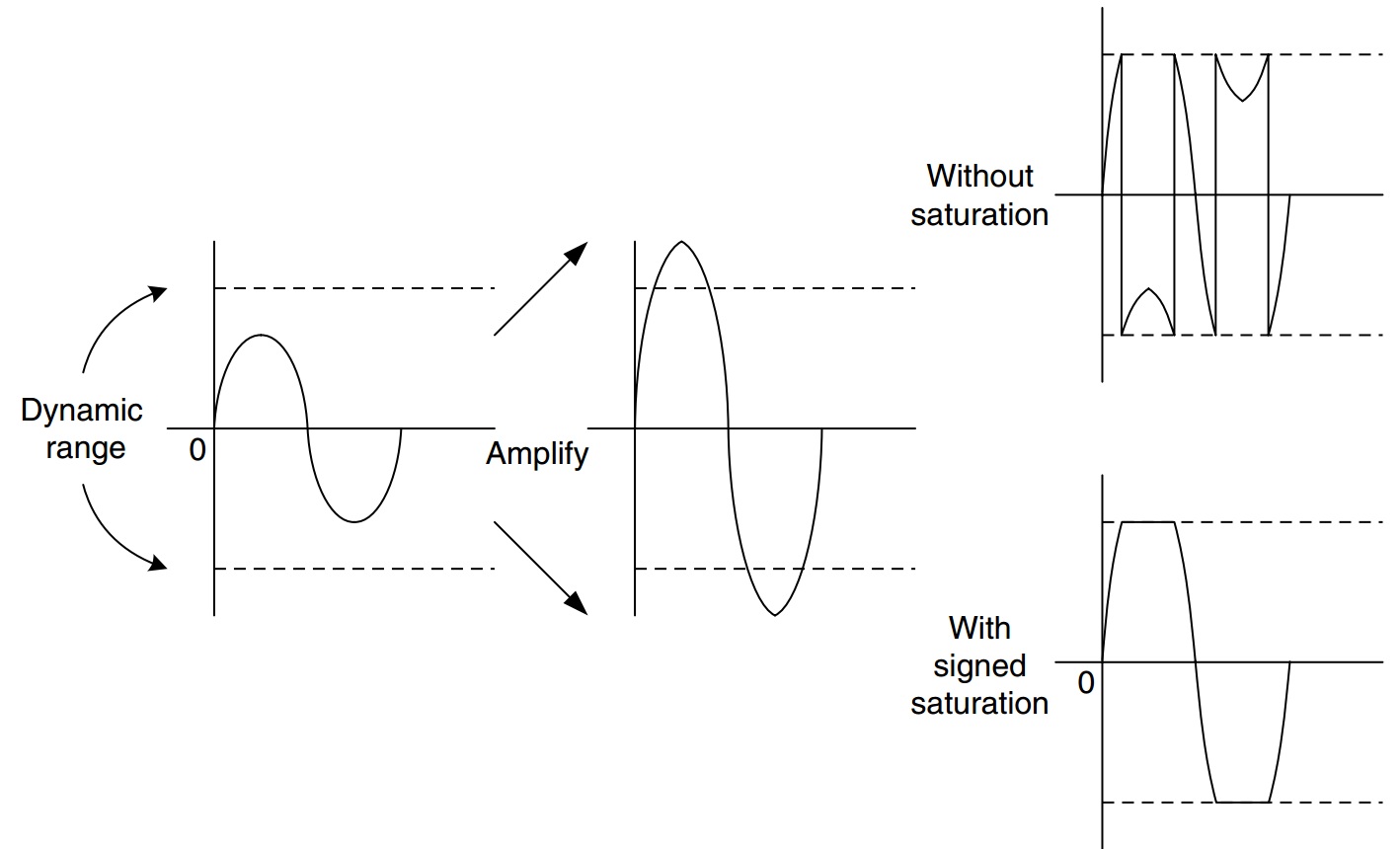

در شکل زیر مشکل سرریز شدن نتیجه محاسبات نشان داده شده است، همانطور که دیده می شود با استفاده از اشباع محاسباتی این مشکل مشابه سیستم های آنالوگ حل می شود.

دستورالعمل های SSAT و USAT :

این دستورالعمل ها برای اعمال اشباع به هر تعداد بیت، پس از تعدادی شیفت ( اختیاری ) استفاده می شود. عمل اشباع محدود کردن خروجی به مقدار حداکثر و حداقل مجاز است. این اشباع همانند اشباع در سیستمهای آنالوگ است.

دستورالعمل SSAT برای حالت با علامت و USAT برای حالت بدون علامت می باشد.

در حالت با علامت محدوده یک عدد n بیتی 2n-1 ≤ x ≤ 2n-1 – 1- است. دستورالعمل SSAT چنانچه نتیجه بیشتر از 2n-1 – 1 شود، مقدار 2n-1 – 1 را بر میگرداند و فلگ Q را 1 می کند و چنانچه نتیجه کمتر از 2n-1 - گردد، مقدار 2n-1_ را به ما می دهد و فلگ Q را 1 می کند. چنانچه نتیجه داخل محدوده باشد و مقدار ورودی و نتیجه مساوی باشند، فلگ Q بدون تغییر می ماند.

در حالت بدون علامت محدوده یک عدد n بیتی بین صفر و 2n – 1 است. دستورالعمل USAT چنانچه نتیجه بیشتر از 2n – 1 گردد، مقدار 2n – 1 را برگردانده و فلگ Q را 1 می کند. همینطور اگر مقدار کمتر از 0 گردد، خروجی 0 را بر می گرداند و فلگ Q را 1 می کند. چنانچه نتیجه داخل محدوده باشد و مقدار ورودی و نتیجه مساوی باشند، فلگ Q بدون تغییر می ماند.

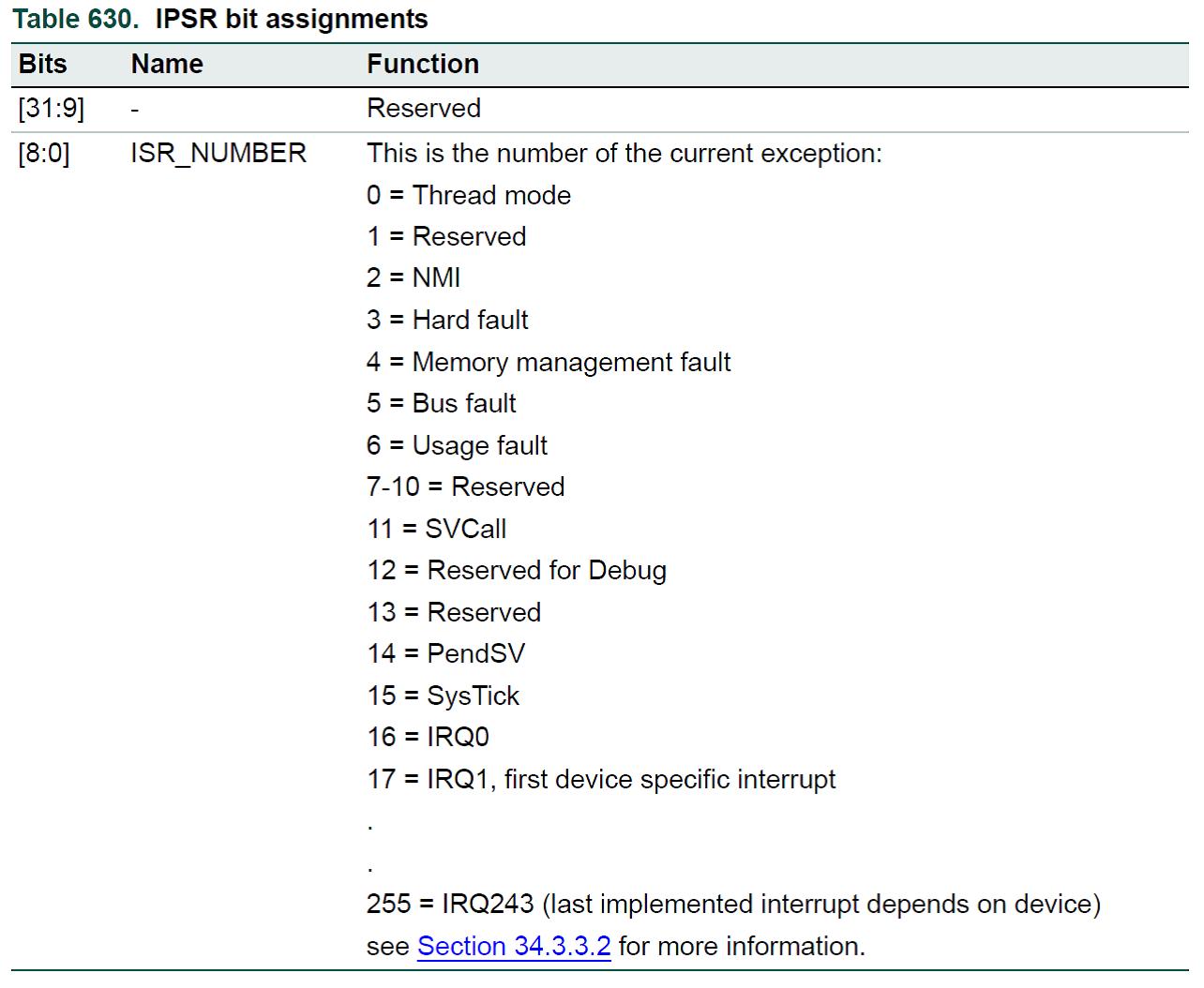

رجیستر وضعیت برنامه وقفه (IPSR) :

رجیستر IPSR شماره استثنا، سرویس وقفه جاری را در بر دارد و بیتهای آن بشرح زیر است.

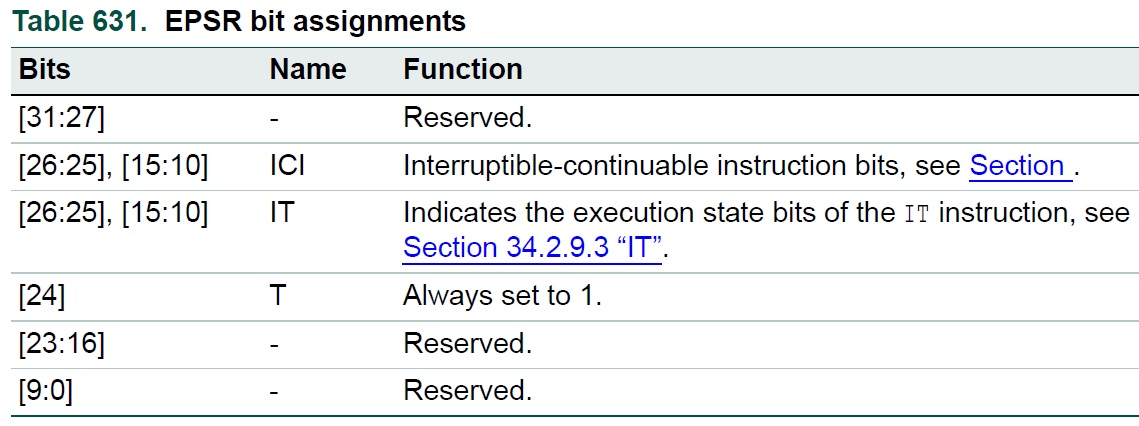

رجیستر وضعیت برنامه اجرایی (EPSR) :

این رجیستر بیت حالت thumb و بیت های وضعیت اجرایی IT و ICI را مطابق جدول 631 دارد.

خواندن از رجیستر EPSR با دستورالعمل MSR هممواره به ما صفر می دهد و نوشتن در آن با دستورالعمل MSR در نرم افزار کاربردی اثری ندارد. تنها اداره کننده خطا می تواند EPSR را بررسی کند.

دستورالعملهای ادامه دار وقفه پذیر ICT) Interruptible-Continuable Instruction) :

در این دستورالعملها چند انتقال و جابجایی داده بین رجیسترها انجام می شود و یا شامل اجرای چند دستورالعمل پیاپی هستند. در Cortex-M3 این امکان وجود دارد، تا در بین این دستورالعملهای طولانی نیز وقفه پذیرفته شود، اما نکته مهم ذخیره مرحله اجرای دستورالعمل، برای دنبال کردن دستورالعمل پس از برگشت از سرویس وقفه است. در ادامه با این دستورالعمل ها آشنا می شویم.

دستورالعمل های LDM و STM برای بار کردن و ذخیره کردن چند رجیستر هستند.

op{addr_mode}{cond} Rn{!}, reglist

addr_mode مشخص می کند که پس از هر انتقال آدرس اضافه (IA) و یا قبل از هر انتقال آدرس کم (DB) شود.

Cond یک شرط اختیاری است.

Rn رجیستری که آدرس دهی حافظه بر اساس آن انجام می شود.

! ( اختیاری ) – اگر ! باشد، آدرس نهایی در رجیستر Rn نوشته می شود.

Reglist – لیستی از یک تا چند رجیستری است، که قرار است بار یا ذخیره شوند. این رجیسترها داخل آکولاد قرار می گیرند و با کاما از یکدیگر جدا می شوند و یک محدوده از رجیسترها را نیز می توان مشخص کرد.

مثال :

LDM R8,{R0,R2,R9} ; LDMIA is a synonym for LDM

{STMDB R1!,{R3-R6,R11,R12

مثال غلط :

STM R5!,{R5,R4,R9} ; Value stored for R5 is unpredictable

LDM R2, {} ; There must be at least one register in the list

حال اگر وقفه در حین اجرای دستوالعمل های LDM یا STM بیاید، پروسسور ابتدا:

- بار یا ذخیره کردن رجیسترها را به طور موقت متوقف می کند.

- رجیستر بعدی را در بیت های [15:12] رجیستر EPSR ذخیره می کند.

پس از اجرای سرویس وقفه، پروسسور :

- به رجیستری که با بیتهای [15:12] مشخص می شود، بر می گردد.

- اجرای دستورالعمل را ادامه می دهد.

وقتی EPSR وضعیت اجرای ICI را دارد، بیت های [26:25,11:10] صفر هستند.

وضعیت اجرای دستورالعمل (If-Then (IT :

دستورالعمل IT یک دستورالعمل شرطی است. دستورالعمل IT تا چهار دستورالعمل بعد از خود را می تواند شرطی کند. شرط می توان برای تمام دستورالعمل ها یکسان و یا بعضی بر عکس باشند.دستورالعملهای شرطی بعد از دستورالعمل IT تشکیل یک بلوک IT می دهند.

IT{x{y{z}}} cond

Cond – شرط اولین دستورالعمل در بلوک IT را مشخص می کند.

X - شرط دومین دستورالعمل در بلوک IT را مشخص می کند. اگر T باشد cond به این دستورالعمل اعمال می شود و اگر E باشد عکس cond به این دستورالعمل اعمال می شود.

y- شرط سومین دستورالعمل در بلوک IT را مشخص می کند. . اگر T باشد cond به این دستورالعمل اعمال می شود و اگر E باشد عکس cond به این دستورالعمل اعمال می شود.

Z - شرط چهارمین دستورالعمل در بلوک IT را مشخص می کند. . اگر T باشد cond به این دستورالعمل اعمال می شود و اگر E باشد عکس cond به این دستورالعمل اعمال می شود.

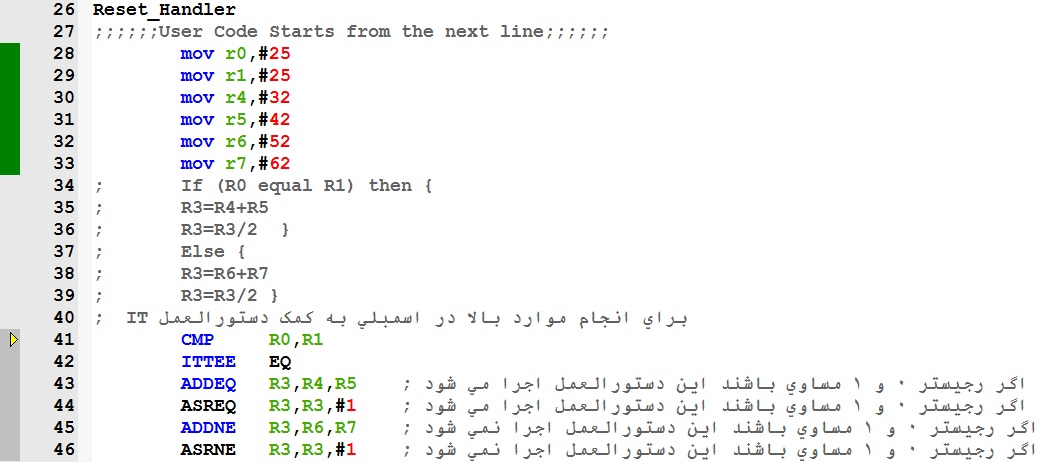

مثال 1 :

برای مثال شما می خواهید برنامه اجرای کدهای زیر را بنویسید:

} If (R0 equal R1) then

R3=R4+R5

{ R3=R3/2

} Else

R3=R6+R7

{ R3=R3/2

در اسمبلی با کمک دستورالعمل IT به شکل روبرو نوشته می شود :

CMP R0,R1

ITTEE EQ

ADDEQ R3,R4,R5

ASREQ R3,R3,#1

ADDNE R3,R6,R7

ASRNE R3,R3,#1

مثال 2 : تبدیل عدد هگز به اسکی

; Convert R0 hex value (0 to 15) into ASCII ('0'-'9', 'A'-'F')

CMP R0, #9

ITE GT ; Next 2 instructions are conditional

ADDGT R1, R0, #55 ; Convert 0xA -> 'A'

ADDLE R1, R0, #48 ; Convert 0x0 -> '0'

اگر دستورالعمل های LDM و STM در بلوک IT آمده باشند و در حین اجرای آن ها وقفه بیاید، این دستورالعملها کنسل و پس از برگشت وقفه مجددا از ابتدا اجرا می شوند. چون بیتهای وضعیت IT و ICT در رجیستر EPSR مشترک هستند.

رجیسترهای پوشش استثنا Exception mask register

این رجیسترها برای غیر فعال کردن استثنا ها و وقفه ها از طرف پروسسور می باشند. برای دسترسی به این رجیسترها از دستورالعمل های MSR و MRS می توان استفاده کرد.

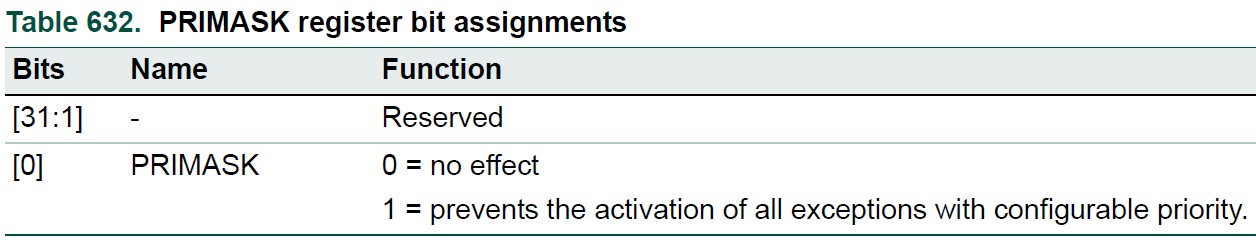

رجیستر پوشش اولویت (Priority Mask Register (PRIMASK

این رجیستر جلوی تمام استثناهایی که اولویت وقفه آن قابل تنظیم است را می گیرد. این بدان معنی است، که جلوی وقفه هایی که اولویت آن ها ثابت است گرفته نمی شود، پس انتظار داریم تمام وقفه ها غیر از NMI و خطاهای شدید (Hard Fault) غیر فعال شوند.

بیت های این رجیستر بشرح زیر است:

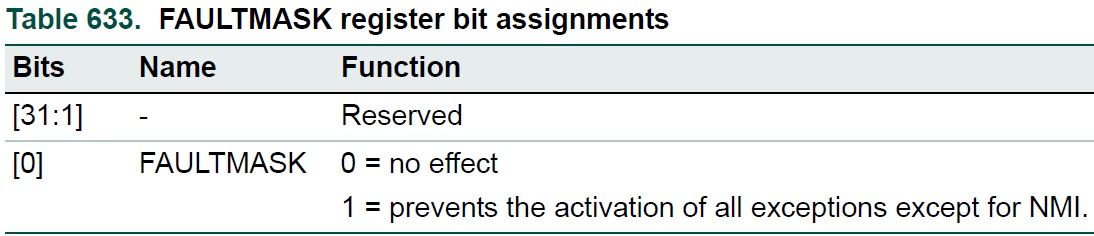

رجیستر پوشش خطا (Fault Mask Register (FAULTMASK

با این رجیستر تمام استثناها غیر از NMI را می توان غیر فعال کرد. بیت های این رجیستر بشرح زیر است:

پروسسور بیت 0 رجیستر FAULTMASK را هنگام خروج از هر سرویس استثنا ( غیر از NMI ) را 0 می کند.

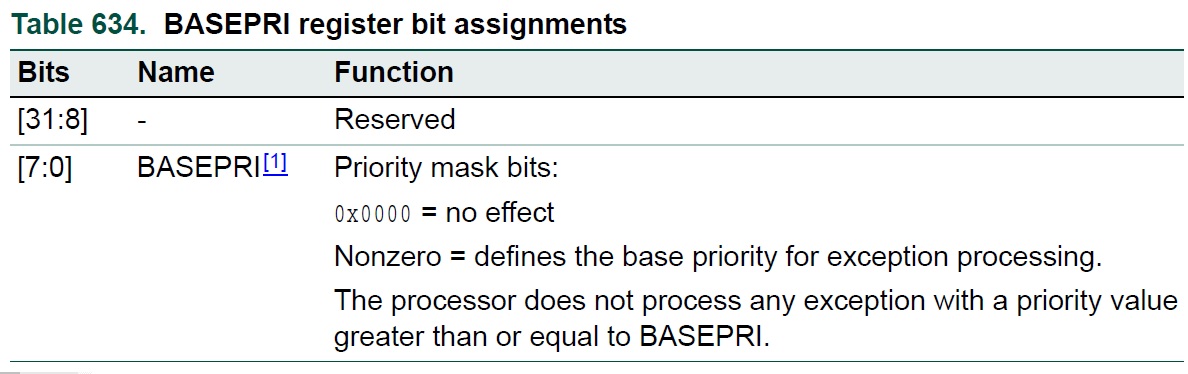

رجیستر پوشش وقفه بر اساس اولویت (Base Priority Mask Register (BASEPRI

رجیستر BASEPRI حداقل اولویت لازم برای قبول اجرای استثنا را تعیین می کند. وقتی به رجیستر BASEPRI یک مقدار غیر 0 داده شود، تمام استثناهای با اولویت کمتر یا مساوی آن غیر فعال می شوند. ترتیب بیت های این رجیستر به شرح زیر است:

همانطور که می بینید، بیت های فوق مشابه فیلد اولویت در رجیسترهای اولویت وقفه است. رجیستر کنترل CONTROL

رجیستر کنترل CONTROL

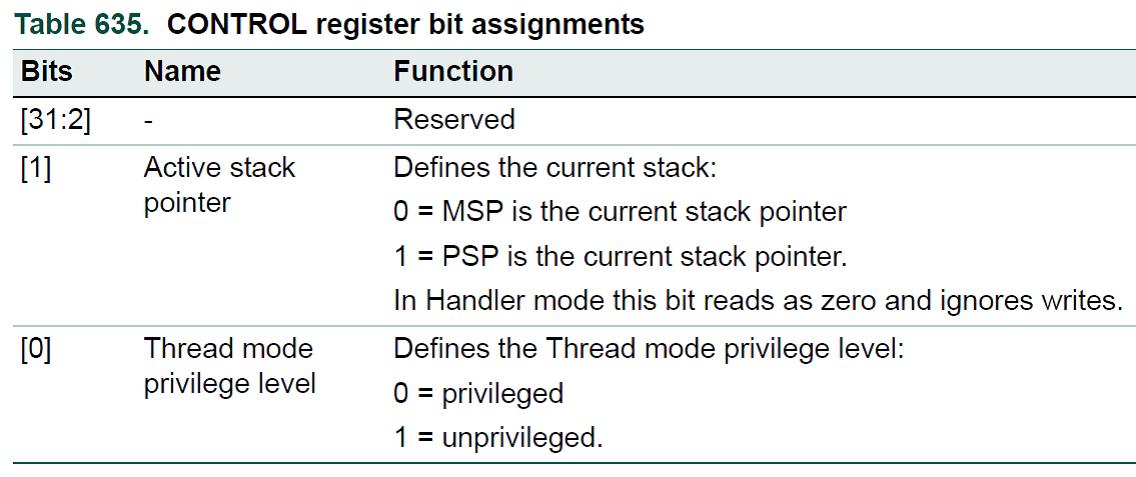

رجیستر کنترل SP استفاده شده و همینطور سطح امتیاز برنامه اجرایی را در حالت ترد مشخص می کند. . ترتیب بیت های این رجیستر به شرح زیر است:

توجه داشته باشید در حالت اجرای استثنا همواره MSP استفاده می شود و نوشتن در رجیستر کنترل برای انتخاب SP فعال بی فایده است. مکانیزم ورود و خروج از استثنا رجیستر کنترل را بروز می کند.

توجه داشته باشید در حالت اجرای استثنا همواره MSP استفاده می شود و نوشتن در رجیستر کنترل برای انتخاب SP فعال بی فایده است. مکانیزم ورود و خروج از استثنا رجیستر کنترل را بروز می کند.

در محیط OS ، پیشنهاد می شود تردها در مد ترد از PSP و برنامه هسته و استثناها از MSP استفاده کنند.

به صورت پیش فرض مد ترد از MSP استفاده می کند و برای تغییر آن به PSP از دسنورالعمل MSR استفاده می شود.

توجه: در هنگام تغییر SP ، نرم افزار باید بلافاصله دستورالعمل ISB را بعد از MSR اجرا کند. این کار استفاده از SP جدید را تضمین می کند.